三星半导体在CFMS 2024分享移动、PC、服务器的创新技术和存储解决方案

深圳2024年3月20日 /美通社/ -- 在2024年CFMS闪存市场峰会上,三星半导体展示了其面向PC、移动端和服务器的多样化创新存储解决方案。三星电子执行副总裁兼解决方案产品工程师团队负责人吴和锡(Hwaseok Oh),发表了题为"与客户同行,共筑创新之路"的演讲。

三星电子执行副总裁兼解决方案产品工程师团队负责人吴和锡(Hwaseok Oh)发表题为“与客户同行,共筑创新之路”演讲

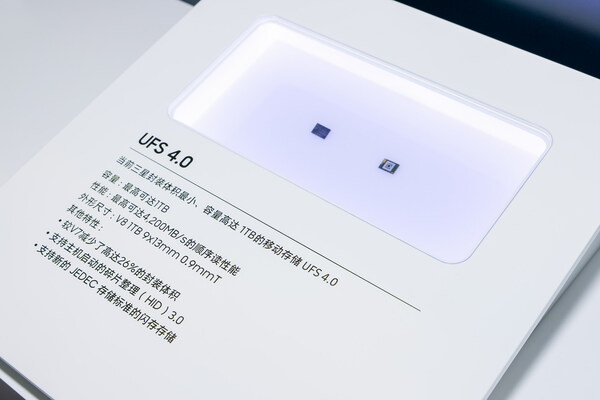

在演讲中,吴和锡强调了推动存储创新的重要性,以及如何通过协同合作克服变革中出现的挑战,并呼吁业界和客户共同携手推动技术进步。峰会上,三星半导体展出了面向移动端的JEDEC最新技术规格的UFS 4.0存储,为加速服务器提供的PM9D3a, 以及基于CXL的创新内存池技术的CMM-D, 和针对AI和MI开发的基于CXL技术的混合式存储解决方案的CMM-H。

在本次演讲中,三星半导体着重介绍了围绕与客户携手合作实现的几个存储领域的技术创新。三星在介绍QLC UFS的技术进展时,要与包括客户在内的生态系统各方参与者开展紧密的合作。继三星在2023年推出QLC UFS以后,现已准备批量生产。虽然QLC技术目前仍然处于早期阶段,但三星QLC性能通过加入全新的TW2.0和HID技术,并且从纵向发力,不断优化主机系统,提升用户应用水平,使QLC产品在实际工作中表现稳定,给用户带来优异的性能。

三星电子执行副总裁兼解决方案产品工程师团队负责人吴和锡(Hwaseok Oh)分享移动,PC,服务器的创新技术和存储解决方案

为了满足日渐增长的端侧(End-to-End)人工智能的需求,实现大语言模型的端侧运行,三星半导体计划提升UFS接口速度并正在研发一款使用UFS 4.0技术的新产品,将通道数量从目前的2路提升到4路。同时,三星半导体也在积极参与UFS 5.0标准的讨论,期望与移动公司和AP公司共同促进UFS 4.0 4通道和UFS 5.0的合作。

UFS 4.0是目前三星封装体积最小、容量高达 1TB的移动存储

在面向PC存储方面,三星半导体介绍了在PCIe 4.0接口环境下表现优异的PM9C1a。

此外,为迎接PCIe5.0时代,三星半导体结合数据中心的先进经验,计划将PCIe 5.0应用于PC存储。

PM9D3a是使用目前三星最先进的PCIe 5.0的固态硬盘,适用于大型数据运算,帮助加速数据中心。 三星半导体准备在多方面为客户提供支持,以帮助PC客户在数据中心部署支持PCIe5.0的SSD。演讲中,三星半导体还提出了FDP技术,即通过控制数据布局来延长设备使用寿命。目前,FDP已经成为当下的解决方案,且已经具备了构建生态系统的四大要素,一是被批准成为NVMe标准,二是主机驱动程序已包含在Linux内核并已分发,三是推出全球首个支持FDP的SSD产品,最后三星开展通过案例研究证明了其在CacheLib应用中的有效性。基于这项技术,三星半导体已经与客户展开合作,并计划通过后续产品提升性能、强化特点提供更多支持,有望构建强大生态系统。

三星半导体还指出,目前搭载了DRAM的CXL产品很受欢迎,已成为新的技术范畴。三星第一代CMM-D搭载了支持CXL2.0的SoC的,计划在2025年发布搭载第二代控制器、容量为128GB的新产品。与此同时,三星还在不断研发同时使用NAND和DRAM的混合式CXL存储模组架构,即针对AI和ML系统使用的CMM-H。

最后三星呼吁客户积极参与高质量的测试数据收集,推动技术进步。 三星半导体将持续与客户紧密合作,共同推动各行业迈向智能化转型的新时代。